10.2

Synchronní čítače

V synchronním čítači reagují všechny klopné obvody na vstupní stavy ve stejný okamžik, tj. synchronně.

+

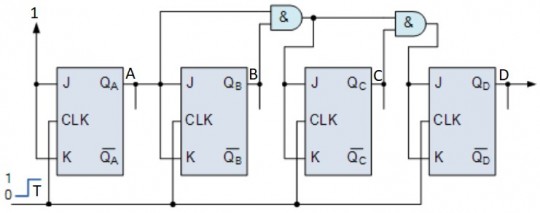

Obr. 88. Synchronní čítač s JK klopnými obvody

Na vstupy J a K klopného obvodu A je připojen signál 1, aby se obvod překlápěl každou sestupnou hranou taktovacích impulzů T přiváděných na hodinový vstup CLK. Klopný obvod B se překlopí, je-li na jeho vstupech J, K stav A=1. Klopný obvod C může být překlopen, jsou-li obvody A, B nastaveny, tj. je-li A AND B=1, což nastane při čtvrtém, osmém, dvanáctém a šestnáctém impulzu (od výchozího stavu). Podmínkou pro překlopení (z 0 do 1) klopného obvodu D je nastavení (stav 1) obvodů A, B a C, což nastane jen při osmém a při šestnáctém impulzu.

+

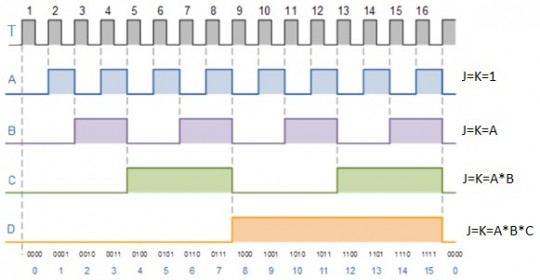

Obr. 89. Synchronní čtyřbitový čítač-časový diagram

+

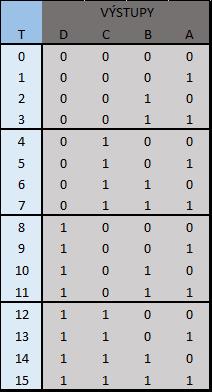

Obr. 90. Synchronní čtyřbitový čítač-pravdivostní tabulka

10.2.1

Synchronní čítač BCD

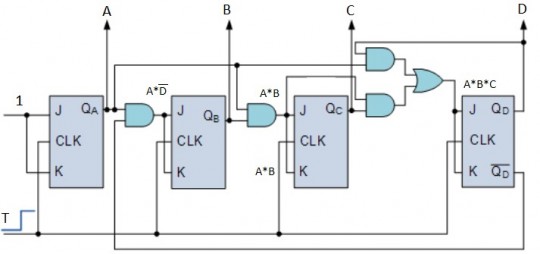

Čítač BCD je po deseti impulzech od výchozího stavu opět vynulován, tj. vrácen do výchozího stavu. Toto je zajištěno logickými obvody, jejichž funkce je popsána logickými výrazy na vstupech klopných obvodů JK. První v pořadí klopný obvod A je překlápěn každou sestupnou hranou, protože jsou oba nastavovací vstupy J, K nastaveny na 1. Klopný obvod B je překlopen, jen je-li A=1 a D =0. Proto není obvod B desátým impulzem nastaven. Obvod C je přednastaven výstupy obvodů A a B. Může být překlopen jen v případě, že A=1 a B=1. Klopný obvod D může být překlopen jen v případě, že jsou nastaveny zbývající obvody, tj. při A=1, B=1 a C=1. Při stavu A=1 při desátém impulzu bude obvod D (při nastavení K=1, J=0) opět nulován.

+

Obr. 91. Synchronní čítač BCD s JK klopnými obvody