2.1

Bistabilní klopný obvod RS

Definice

Název RS je odvozen z pojmenování dvojice vstupů obvodu, reset a set.

Obvod RS tedy obsahuje dvojici vstupů,

(reset) a

(set), a dvojici výstupů

a

. Základní zapojení klopného obvodu RS získáme pomocí dvojice hradel NOR a dvojice zpětných vazeb, jak ukazuje obrázek 9.

+

Obr. 9. Základní realizace klopného obvodu RS.

Souhrn

Funkci obvodu můžeme popsat nastavením jednotlivých kombinací hodnot na jeho vstupy:

- Ve výchozím stavu nastavíme S = logická 1 a R = logická 0, pak na výstupu = logická 1 a = logická 0. Obvod provádí jedničkovou transformaci.

- Poté vstup S změníme na logickou 0, výstupy obvodu se nezmění. Obvod provádí paměťovou transformaci.

- Následně vstup S ponecháme na hodnotě logická 0 a na vstup R nastavíme logickou 1, na výstupu = logická 0, výstup = logická 1. Obvod provádí nulovou transformaci.

- Pak vstup R vrátíme zpět na hodnotu logická 0, výstupy se nezmění. Obvod provádí paměťovou transformaci.

- Nakonec oba dva vstupy S i R nastavíme na hodnotu logická 1 současně – výstup obvodu není určen, jde o tzv. zakázaný stav obvodu!

Chování klopného obvodu RS můžeme rovněž popsat tabulkou 1.

Tabulka 1. Pravdivostní tabulka klopného obvodu RS.

R | S | Qt+1 | transformace |

0 | 0 | Qt | M |

0 | 1 | 1 | 1 |

1 | 0 | 0 | 0 |

1 | 1 | zakázaný stav | |

A také grafem přechodů na obrázku 10.

+

Obr. 10. Graf přechodů klopného obvodu RS.

Definice

Zakázaný stav klopného obvodu RS představuje nepovolenou vstupní kombinaci R = S = 1.

Při této kombinaci vstupních hodnot totiž není jednoznačně určen výstup obvodu. K tomu vedou dva důvody. Jednak při praktické realizaci klopného obvodu RS pomocí dvojice hradel, která nemají nikdy zcela totožné doby zpoždění, není zřejmé, které hradlo překlopí jako první a které až jako druhé s větším zpožděním. Druhým důvodem je fakt, že v případě ideálních logických hradel s nulovým zpožděním by pro výstupy klopného obvodu RS platilo

. Tudíž by nebyla splněna základní podmínka funkce BKO, že invertovaný výstup musí být vždy negací výstupu přímého.

Kromě realizace pomocí hradel NOR, lze klopný obvod RS realizovat také pomocí hradel NAND, jak ukazuje obrázek 11. V tom případě ale budou vstupy obvodu negované, tzn. místo na úroveň logická 1 budou spouštěny na úroveň logická 0.

+

Obr. 11. Realizace klopného obvodu RS pomocí hradel NAND.

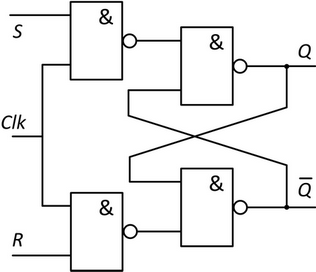

Klopný obvod RS můžeme rovněž realizovat v synchronní variantě. V tom případě potřebujeme do obvodu přidat vstup pro periodický hodinový signál Clk, na jehož úroveň (hladinový obvod RS) nebo hranu (hranový obvod RS) bude funkce klopného obvodu RS vykonávána. V případě pozitivní logiky (spouštění obvodu na úroveň logická 1 nebo vzestupnou hranu hodinového signálu Clk) přidáme do zapojení klopného obvodu RS pomocí hradel NAND další dvojici hradel, a získáme tak zapojení jako na obrázku 12.

+

Obr. 12. Synchronní varianta klopného obvodu RS.

Protože je klopný obvod RS často využíván v různých zapojeních logických obvodů, byla pro něho standardizována schématická značka, která je v synchronní i asynchronní variantě uvedena na obrázku 13.

+

Obr. 13. Obvodové značky synchronního a asynchronního klopného obvodu RS.

Zajímavost

Ve schématech elektronických obvodů se obecně pro rozlišení nedatových, např. hodinových, vstupů obvodů používá značka „zobáčku“.