2.3

Klopný obvod D

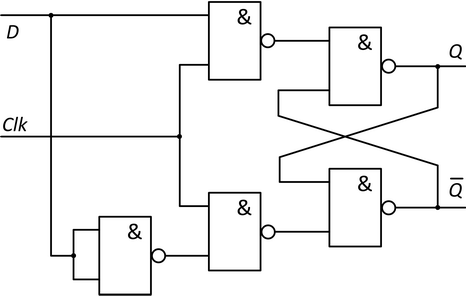

Klopný obvod D získáme, když upravíme zapojení synchronního obvodu RS na obrázku 12 tak, že do vstupu R připojíme negaci vstupu S. Klopný obvod D má tak pouze jeden datový vstup D a hodinový vstup Clk. Jeho schéma nalezneme na obrázku 19.

+

Obr. 19. Schéma zapojení klopného obvodu D.

Díky tomu, že obvod D je v zásadě synchronní klopný obvod RS, pro který platí

, vyjdeme z pravdivostní tabulky klopného obvodu RS (tabulka 1) a vybereme z ní pouze řádky, kdy jsou oba vstupy navzájem opačné. Pro klopný obvod D tak sestavíme pravdivostní tabulku 3.

Tabulka 3. Pravdivostní tabulka klopného obvodu D.

D | Qt+1 | transformace |

1 | 1 | 1 |

0 | 0 | 0 |

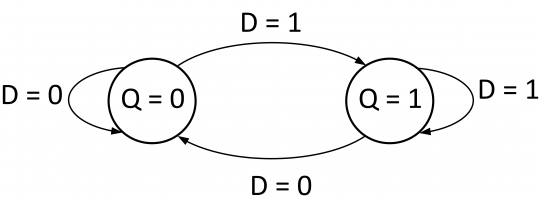

Tabulce odpovídá graf přechodů klopného obvodu D na obrázku 20.

+

Obr. 20. Orientovaný graf přechodů klopného obvodu D.

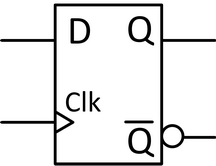

A jeho obvodová značka na obrázku 21.

+

Obr. 21. Schematická značka klopného obvodu D.

Zajímavost

Klopný obvod D se v podstatě chová jako jednoduchá dočasná jednobitová paměť. Obvod kopíruje vstupní hodnotu D na svůj výstup Q (a negovanou na výstup

) a tuto hodnotu si uchovává do svého dalšího překlopení (příchodu hrany či hladiny Clk). Funguje tak vlastně i jako zpožďovací člen. Označení klopný obvod D tedy vychází z principu jeho činnosti v angličtině – Data či Delay.

Poznámka

V případě hladinového klopného obvodu D může vzniknout problém označovaný jako tzv. ripple-through. V době trvání hladiny hodinového signálu Clk, během které je klopný obvod D aktivní, se v případě vícenásobné změny vstupního datového signálu D všechny tyto změny přenesou v této době ihned na výstup obvodu. Na výstupu se tak může vícekrát změnit hodnota a zůstane zde do příští aktivní doby ta z nich, která se na vstupu D objeví jako poslední před skončením aktivní doby (změny hladiny signálu Clk). Jako řešení se obvykle používá zkrácení aktivní doby klopného obvodu D tím, že se k jeho vstupu Clk připojí sudý počet hradel NAND, jejichž zpoždění posune dobu trvání aktivní hladiny Clk mimo dobu trvání změn na vstupu D.

Klopný obvod D (ale i ostatní klopné obvody, např. JK) lze vybavit tzv. asynchronními vstupy.

Definice

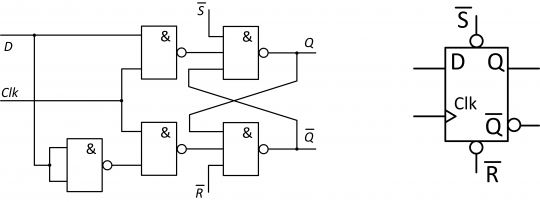

Asynchronní vstupy vzniknou přidáním dodatečných vstupů do dvojice hradel NAND, která tvoří výstup klopného obvodu a která jsou navzájem propojena vazbami, jak ukazuje obrázek 22.

+

Obr. 22. Zapojení klopného obvodu D s asynchronními vstupy (vlevo) a jeho schematická značka (vpravo).

Tato dvojice vstupů

a

je označována jako asynchronní z toho důvodu, že jejich aktivace není vázána na stav hodinového signálu Clk a tyto vstupy tak mohou být aktivovány kdykoliv (asynchronně). Vstup

bývá označován jako preset (přednastavení) a vstup

jako clear (nulování).

Jak z označení

a

vyplývá, jsou tyto vstupy aktivní v logické 0, a nikoliv v logické 1.

Jejich funkce navíc vždy převáží (má prioritu) nad hodnotou vstupu D, neboť v případě součinových hradel NAND se uplatní zákon agresivity nuly.

Tyto asynchronní vstupy jsou často využívány např. pro asynchronní nulování sekvenčních obvodů, např. čítačů či stavových automatů, realizovaných pomocí klopných obvodů, nebo pro přednastavení určité hodnoty v čítači (např. odečet směrem dolů).